�������ַŴ���

ת�Ե��ӹ�����

���Ժ���ʷ�ع�

���������Ŵ�����SHA�Ǵ����ݲɼ�ϵͳ�Ĺؼ���ɲ��֣�����ģ���źŲ���ijЩ�������������ģ��ת�����б����źŲ��䡣SHA�������·��Ҫ��dz��ߣ�������ӡˢ��·�����ͨ�����ijЩ���Կ��ܻ����벻���ؽ���SHA���ܡ�

��SHA���ADCʹ��ʱ�����û����ã���SHA���ܶԸ���ϵ����嶯̬����������Ҫ����ȷ��ϵͳ��SFDR��SNR�Ȳ�������������Ҫ���á�

��Ȼ�����SHA�����Ѿ����ɵ�����ADC�У����˽����������ԭ�������˽�ADC��̬����ʮ����Ҫ��

���������������ڲ���������٣�ģʽʱ���������������仯������֮������ں�С����ѹƫ���Ҳ������ڲ���ģʽ�²���ȫ���������SHA����������ڱ����ڼ��Ǿ�ȷ�ģ���AD684��AD781��AD783�������IJ���������������ϸ���˵���������ø������ܵIJ���������Ӧ����Ϊ���ٱ��ֵ�·������ʵ��Ӧ���У���Щ������Ի���ʹ�á�

SHA�����Ӧ����������ת���ڼ佫ADC�����뱣��Ϊ�㶨ֵ���������ࣨ������ȫ�������͵�ADC��Ϊ����ת�����̱��ƻ���ת���ڼ�����ı仯���ô���1 LSB����ͶԴ���ADC�����˷dz��͵�����Ƶ����ֵ������Ҫ�����SHA�Ա���ÿ��ת���ڼ�����벻�䡣

�ع���ʷ��һ����Ȥ����ʵ�ǣ�A. H. Reeves����������PCMר����1939���ο�����1����������һ��5λ6 kSPS����ADC��ģ�������ź�ֱ������һ����չ�����������(PWM)���������ܼ�����PWM�С�����ʵ��������PCM�������о����������������������ܺ���αƽ���ADC���ο�����2 (1948)������һ������������ѹ��������·������50 kSPS��չܲ������ֵ�·��

��1950������ں�1960������ڣ����ž����ȡ����չܣ����Ǹ��ӹ�עADC���õIJ������ֵ�·��1964�꣬����ʵ���ҵ�Gray��Kitsopolos����������Թ�̬���������������������з���������֮һ���ο�����3��������ʵ���ҵ�Edson��Henning��������һ��224 Mbps PCMϵͳ�Ͻ���ʵ��Ľ������ϵͳ����һ��9λADC��һ������12 MSPS�������������ο�����4��5��6��1960�����1970������ڲ������ֵ�·�о��ɹ��Ĵ���֮����

1969�꣬ADI��˾���չ���Pastoriza���������Ƴ����ò���������SHA1��SHA2����·��PC����ʵ�֣�SHA1��0.01%�ɼ�ʱ��Ϊ2 ��s������0.9 W���ɱ�ԼΪ$225��SHA2�ٶȸ��죬0.01%�ɼ�ʱ��Ϊ200 ns������1.7 W���ɱ�ԼΪ$400����������ר�����ͬ����PC����ʵ�ֵ�12λ��αƽ���ADC������

ģ�黯�ͻ�ϼ���Ѹ����̭��PC�������������������IC ADC�����У��繤ҵ��AD574�ȣ��Բ�������������������������70�����80������ڣ�ϵͳ���ʦ��������IJ�������������������ADC���൱�ձ��������Ϊ��ʱ�Ĺ��ռ������������Ǽ�����ͬһоƬ�ϡ�IC SHA����AD582 ��0.01%�ɼ�ʱ��Ϊ4 ��s����AD583 ��0.01%�ɼ�ʱ��Ϊ6 ��s����AD585 ��14λ���ȵIJɼ�ʱ��Ϊ3 ��s���ȣ�������������70�����80����ĵ����г���

���SHA����HTS-0025��0.1%�ɼ�ʱ��Ϊ25 ns����HTC-0300��0.01%�ɼ�ʱ��Ϊ200 ns����AD386��16λ���ȵIJɼ�ʱ��Ϊ25 ��s���ȣ�������ڸ��ٸ߶��г�����1995�꣬ADI��˾��Ը���Ӧ���Ƴ��˴�Լ20��������ֲ�Ʒ���������и���IC��AD9100/AD9101��0.01%�ɼ�ʱ��Ϊ10 ns����AD684 ����ͨ����0.01%�ɼ�ʱ��Ϊ1 ��s����AD783 ��0.01%�ɼ�ʱ��Ϊ250 ns����

Ȼ����ͬʱ�ڵ�ADC����Ѹ�ͷ�չ������ADC��������SHA��������ADC�������������ָ������ȻҲ������ʹ�á��¹��յĿ������������ٻ���˫���Թ��պ��Ƚ���CMOS���գ�ʹ�ü���SHA���ܳ�Ϊ���ܡ���ʵ�ϣ����ڣ�2003�꣩����ADC�Ѿ��dz��ռ������ܻ�ӭ������������Ҫ������SHA��

���˳ߴ��С���ɱ����ͺ��ⲿԪ�����ٵ����Ե��������⣬����ADC����һ����Ҫ���ƣ��Ǿ�������ֱ���ͽ�����������ȫ��ȷ�������Ա������Դ�����ADC�����SHA�����������Ҫȷ�������ڹ�ӿڻ�ʱ�����⡣������SFDR��SNR�ȶ�̬����ʱ����һ������Ϊ�ɹ�

SHA����ʱ������ADCһ��ʹ�ã���ż��Ҳ������DAC�ޱ�������ֵ�첨����ģ���ӳٵ�·��ͬ������ϵͳ�����ݷ���ϵͳ��

SHA��������ԭ��

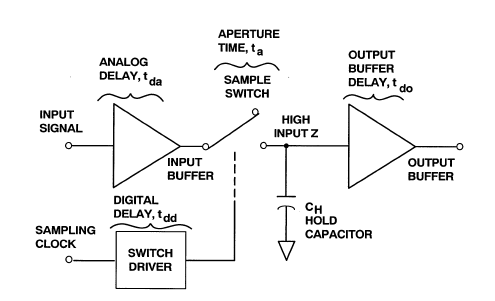

����SHA�ĵ�·ϸ�ڻ�������Σ����д��������������ĸ���Ҫ���֣�����Ŵ����������洢Ԫ�������ݣ�������������Ϳ��ص�·����ͼ1�ĵ���������ʾ��

ͼ1�������������ֵ�·

SHA�ĺ��ġ��������洢Ԫ���ǵ��ݡ�����Ŵ����������룬���ź�Դ�ṩ���迹�����ṩ���������������ֵ��ݳ�硣�ڸ���ģʽ�£����ֵ����ϵĵ�ѹ���棨����٣������źţ���һ�����ӳٺʹ������ƣ����ڱ���ģʽ�£����ضϿ������ݱ��������뻺�����Ͽ�����֮ǰ�ĵ�ѹ������������ֵ����ṩ���迹����ֹ���ֵ�ѹ����ŵ硣���ص�·��������������SHA���洦�ڸ��ٺͱ���ģʽ���л����ơ�

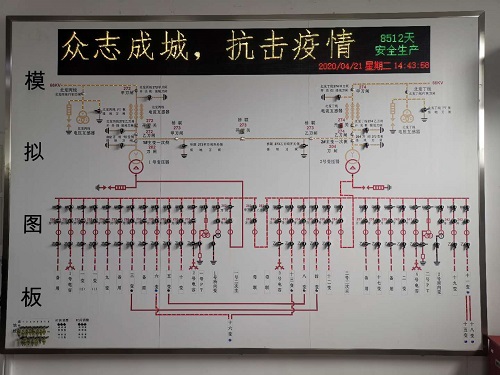

����SHA���������Ĺ�������飺����ģʽ������ת���֡�����ģʽ������ת���١�ͼ2�ܽ�����Щ���ͼ3��ͼ�ⷽʽ��ʾ��SHA��һЩ���Դ������ÿ��ģʽͬʱ�漰��ֱ���ͽ������ܣ����Ҫ��ȷָ��SHA���˽�����ϵͳ�еIJ�����һ���ܸ��ӵ����顣

|

����ģʽ |

��������ת�� |

����ģʽ |

���ֲ���ת�� |

|

��̬ |

��̬ |

��̬ |

|

|

ʧ�� |

������� |

�½� |

|

|

������� |

������������ |

�Ǵ����� |

|

|

������ |

|

������ |

|

|

��̬ |

��̬ |

��̬ |

��̬ |

|

����ʱ�� |

���ӳ�ʱ�� |

��ͨ |

�ɼ�ʱ�� |

|

���� |

������ |

ʧ�� |

���� |

|

ѹ���� |

����˲�� |

���� |

˲�� |

|

ʧ�� |

����ʱ�� |

|

|

|

���� |

|

|

|

ͼ2���������������

ͼ3��������������һЩ���Դ

����ģʽ���

�ڲ���������٣�ģʽ�£�SHAֻ��һ���Ŵ������������ģʽ�µľ�̬�Ͷ�̬�������κ������Ŵ������ơ����ڸ���ģʽ�������½���SHAһ���ָ������ģʽ�µ����ԡ�������ģʽ�µ���Ҫ��������ʧ�������桢�����ԡ�������ѹ���ʡ�����ʱ�䡢ʧ���������Ȼ����ʧ��������ڸ���ģʽ��һ�㲻���ڱ���ģʽ����Ҫ��

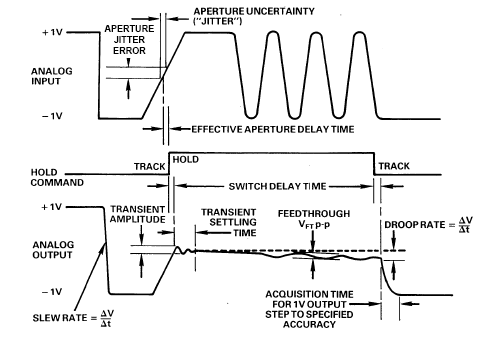

����ת����ģʽ���

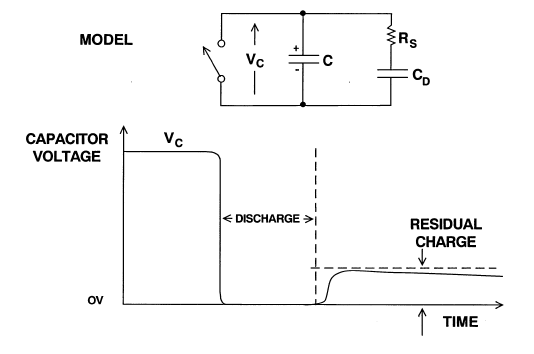

��SHA�Ӹ����л�������ʱ�����ڿ��صķ��������ԣ�һ�������������ͷ��ڱ��ֵ����ϡ���ᵼ�±���ģʽֱ��ʧ����ѹ����Ϊ��������ͼ4��ʾ�����SHA����ADC������������Ϊֱ��ʧ����ѹ������ͨ��ϵͳУ���������������������������źŵ�ƽ��أ����ɴ˲����ķ����Ի����ӱ���ģʽ�µ�ʧ�档

ͨ����߱��ֵ��ݵ�ֵ����Ӧ���ӳ��ɼ�ʱ�䲢���ʹ�����ѹ���ʣ����Լ�С������

�Ӹ����л������ֻ����˲�䣬SHA����������������Χ���������ʱ���Ϊ����ģʽ����ʱ�䡣ż��Ҳ��涨����˲��ķ�ֵ���ȡ�

ͼ4������ת����ģʽ�Ļ��ס�˲��ͽ���ʱ�����

��SHA�ļ�������У�������⡢�������õĿ�������Щ�������Ĺ��SHA������Ķ�̬���������ܹ����ٶϿ����ֵ��������뻺��Ŵ��������ӣ���һ��������ļ��̣������㣩ʱ������Ϊ��ʱ�䡣SHA�ڲ�ʱ��ĸ����������ͼ5��ʾ��

ͼ5��˵���ڲ�ʱ���SHA��·

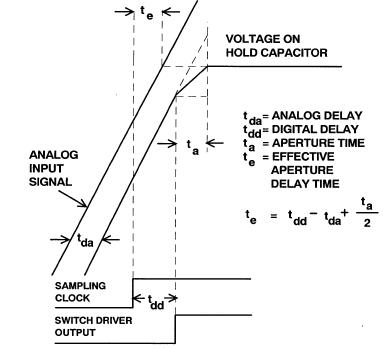

�˼������ʱ���ֵ�ѹ��ʵ��ֵȡ���������źźͿ��ز��������������ͼ6��ʾ��һ������б�ʵ������ź�Ӧ�ñ�������ʱ�������Ϊ�����������Բ���ת���ֻ��Ϳ���˲�䣩�����ձ��ֵ�ֵ�������źŵ��ӳٰ汾�������ǿ��ؿ�ʱ�䷶Χ�ڵ�ƽ��ֵ����ͼ6��ʾ����һ��ģ�ͼ��裬���ֵ����ϵ����յ�ѹֵԼ����Ӧ���ڿ��ص��ź��ڿ��شӵ��迹��Ϊ���迹��ʱ����(ta)�ڵ�ƽ��ֵ��

ͼ6��SHA����

��ģ����ʾ�����ضϿ����������ʱ��(ta)�൱��������SHA�IJ���ʱ��������һ��С�ӳ١����ӳ�Ϊ��������������ֵ��Ҳ�����Ǹ�ֵ������Ϊ��Ч���ӳ�ʱ�䡢���ӳ�ʱ�����ӳ�(te)������Ϊǰ�˻�������ģ����ӳ�(tda)�뿪�������������ӳ�(tdd)��ʱ�����Ͽ�ʱ���һ��(ta/2)����Ч���ӳ�ʱ��ͨ��Ϊ��ֵ���������ʱ���һ��(ta/2)�뿪�������ӳ�(tdd)֮��С��ͨ�����뻺�����Ĵ����ӳ�(tda)������Ҳ�����Ǹ�ֵ����ˣ����ӳٹ��ȷ���������ź�����ڲ���ʱ���ص�ʵ�ʲ���ʱ�䡣

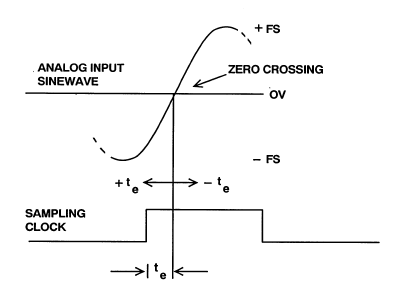

���ӳ�ʱ�����ͨ�����·�������������SHAӦ��һ��˫�������Ҳ��źţ�Ȼ�����ͬ������ʱ���ӳ�ʱ�䣬ʹ��SHA������ڱ����ڼ�Ϊ0���������ʱ�������������Ҳ�ʵ���㽻Խ��֮�������ӳټ�Ϊ���ӳ�ʱ�䣬��ͼ7��ʾ��

ͼ7����Ч���ӳ�ʱ��

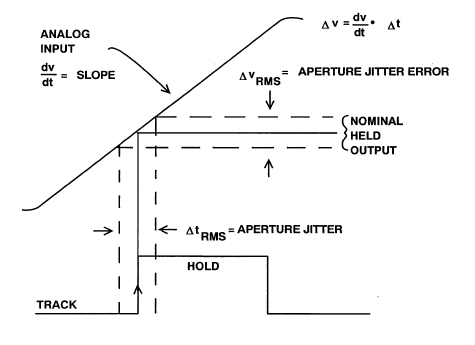

���ӳٲ������������ڲ���ʱ�������ģ�����루ȡ��������ţ�����̶��ӳ����á�������ӳ��д���������仯��������������������Ӧ�ĵ�ѹ����ͼ8��ʾ���ڿ��ضϿ���ʱ�̣�����������仯��Ϊ����ȷ���Ի��������ͨ���þ�����Ƥ��(ps rms)����������Ӧ������ķ�����ģ������ı仯�����йء���Լȶ��Ŀ�����ֵ�������������������dv/dt��߶���ߡ�

ͼ8���������ʱ�Ӷ�����SHA�����Ӱ��

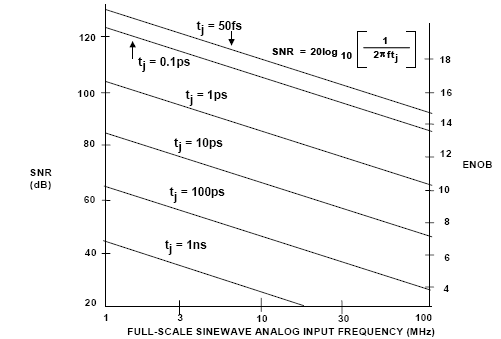

����SHA�Ŀ����������Ҫ�����IJ���ʱ�Ӻ�ģ�������ź�Դ����Ϊ��Щ�ź��ϵĶ�������SHA������������������������Ӱ������ͬ�ġ���ʵ�ϣ�ϵͳ�е����ʱ�����Դ������SHA�������ADC��֮�⣬���ڸ��������ȶ���ʱ�ӡ��źŲ��߲����Լ�û�в������õĽӵغ�ȥ��������¡�SHA������һ��С��50 ps rms������������С��5 ps rms�����ڲ���ADC����������ϸ˵��������IJο�����11�ĵ�5�¡�

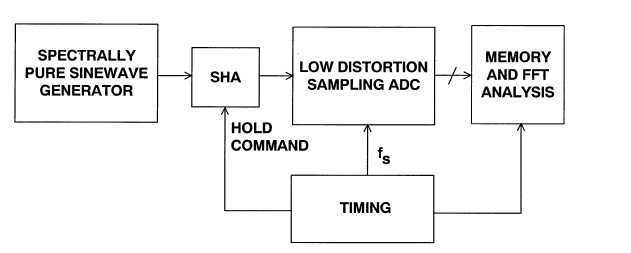

ͼ9��ʾ���ܲ���ʱ�Ӷ��������ݲ���ϵͳ�����(SNR)��Ӱ�졣�ܾ����������ɶ��������ɣ�ʵ��SHA���������������Ҫ��һ�����֡�

ͼ9������ʱ�Ӷ�����SNR��Ӱ��

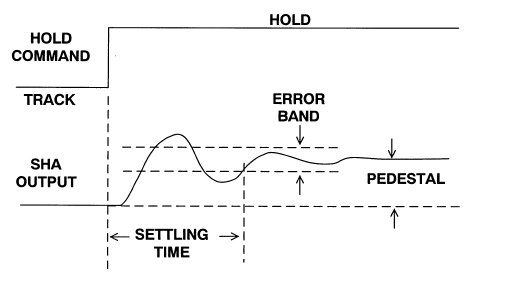

����ģʽ���

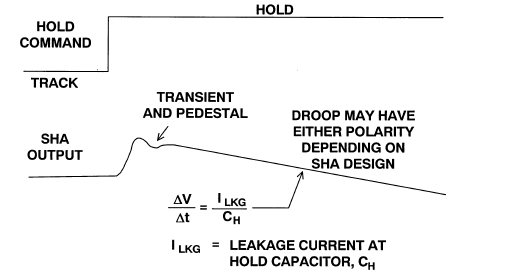

�ڱ���ģʽ�£����ֵ��ݡ����غ�����Ŵ�����ȱ�ݻ������������©����������������ֵ��ݣ����ݻỺ������ŵ磬���ѹ������ͼ10��ʾ�ı仯������ЧӦ��ΪSHA�����ѹ�½�����V/��s��ʾ��ѹ���������ۻ�PC���й©��ʹ���ⲿ����ʱ������й©�ĵ������𣬵������ԭ�����뵼�����ص�©�������������Ŵ�����ƫ�õ��������Խ��ܵ�ѹ��ֵ�ǣ�����������ADCת���ڼ䣬SHA������仯���Ȳ�����½ LSB������ֵ�߶�������ADC�ܹ������ѹ�����ɷ�ƫ�ᣨCMOS���ػ�FET�Ŵ���դ������©����������оƬ�¶�ÿ����10��C�����ͻ����һ��������ζ�Ŵ�+25��C��+125��C��ѹ�������1000����

ͨ����߱��ֵ��ݵ�ֵ���Խ���ѹ��������Ҳ���ӳ��ɼ�ʱ�䲢������ģʽ�µĴ���������ΪADCһ���ֵ��ִ�IC�������ֵ�·�У��������ò�ּ�������Сѹ��ЧӦ��

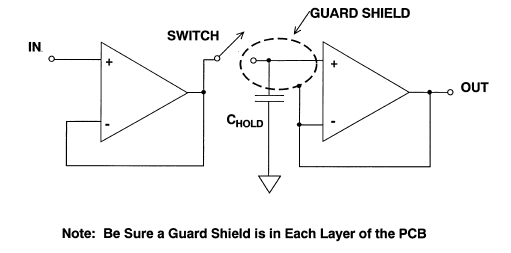

ͼ10������ģʽѹ��

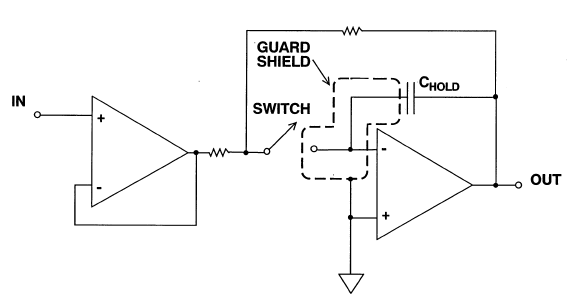

��SHAʹ��С���ֵ���ʱ����ʹ��С��©����Ҳ�����������ص�ѹ����PCB��©��������ͨ�������ʹ�ñ���������С������������һ���ɵ��幹�ɵĻ�������Χһ�����нڵ㲢���ڵȵ�λ���������û�е�ѹ����˲�����©������������ͬ��Ӧ���У���ͼ11��ʾ�����뽫��������������ȷ�ĵ�λ��������ϵı��������Դ���ʵ�ʵĵص�λ��ͼ12����PCB���ϵı�������Զ����������裬���PCB���˱��붼���ϱ��������ڶ����ϣ����в㶼Ӧ���б�������

ͼ11�����뱣�ֵ�����ͬ�ĵ�ѹ�����������Խ��͵�·��й©

ͼ12�������SHA�����ʹ�÷�����

SHA���ֵ��ݵ�й©����ܵͣ�������һ������Ҳͬ����Ҫ������ǡ��͵�������ա������һ�����ݳ�硢�ŵ�Ȼ��·������ָ�һЩ��ɣ���ͼ13��ʾ�����������Ϊ����������ա������ᵼ����һ�������IJ��ಿ����Ⱦ�����������ҿ���������ʮ��������mV���������˿��ܻ�ʹSHA���������ؽ��͡�

ͼ13�����������

��ͬ�ĵ��ݲ��Ͼ��в�ͬ�ĵ����������������ʵ�������⣨й©Ҳ�ܸߣ���ijЩ��K�մɵ���Ҳ�ܲ����ĸ���۱���ϩ�;۱�ϩ����һ��Ϻá��ź����ǣ���Ʒ���β�ͬ�����������Ҳ��������ͬ����ʱ���۱���ϩ�;۱�ϩ����Ҳ����������Ӱ�졣��ˣ���������SHAӦ�õĵ���ʱ������30-50%��Ԥ�������ǵģ�����Ӧ�����������̱�֤�����е͵�������յ������������ǹ���һ����Ϊ�������������Ե�ij����ݡ�

SHA����ɢ���ݿ��ܻ����������������ڱ����ڼ���ϵ����������ЧӦ��Ϊ��ͨ��ȡ��������Ƶ�ʺͷ��ȡ������ͨ��SHA������źŷ��ȴ���½ LSB��ADC�ͻᷢ��ת������

����SHA�У�ʧ����ڸ���ģʽ�¹涨������ģʽʧ�泣��Զ���ڱ���ģʽʧ�档����ģʽʧ�治����������������ķ����ԣ�������ADCʱ����������ӳSHA�����ܡ��ִ�SHA���ر��Ǹ���SHA��ͨ���涨����ģʽ�µ�ʧ�档����ģʽʧ���������ģ��Ƶ������������������ģʽʧ��Ӧ������ͼ14��ʾ�����ּ������в�������һ��Ƶ�״��������Ҳ�Ӧ����SHA��һ����ʧ�����ADC�ڱ���ʱ���Ҫ����ʱ��SHA����������ֻ���Ȼ���ADC���ִ��FFT������������ʧ��ɷ֡�

ͼ14����������ģʽʧ��

�ڸ���ģʽ�£�SHA�����Ĺ涨�Ͳ�����Ŵ������ơ����ֵ����ģʽ��������ʾ����������Ȼ�����6.6ת���ɾ�����ֵ������ģʽ����������Ƶ���ܶ�(nV/��Hz)����ʾ�������ö�����ڵľ�����ֵ����ʾ����������˵��������ģʽ�������������ģʽ�����ϲ��Եó��������������ЩSHA�涨�������������ģʽ���������а�������ģʽ������

����ת����ģʽ���

��SHA�ӱ����л�������ʱ�����������»�ȡ�����źţ������ź��ڱ���ģʽ�ڼ�����Ѿ�����������ԾǨ������ȡʱ����ָSHA�ӱ����л�������ʱ�����»�ȡ�źŲ��ﵽĿ�꾫�������ʱ��������ʱ������ʼ�ڲ���ʱ���ص�50%�㣬������SHA�����ѹ���ڶ��������ʱ��ͨ���涨0.1%��0.01%ʱ�䣩��ijЩSHA���涨����ڱ��ֵ��ݵ�ѹ�Ļ�ȡʱ�䣬������������������ӳٺͽ���ʱ�䡣���ֵ��ݻ�ȡʱ���������ڸ���Ӧ�ã�������Ӧ���У�����Ϊ����ģʽ������ܵ��ʱ�䡣��Ȼ���������������ʱ���������С�ڱ���ʱ�䡣

��ȡʱ����������ִ����ֲ���ʾ����(DSO)������ӫ��ʾ����(DPO)ֱ�Ӳ�������Щʾ�����Դ���������С�

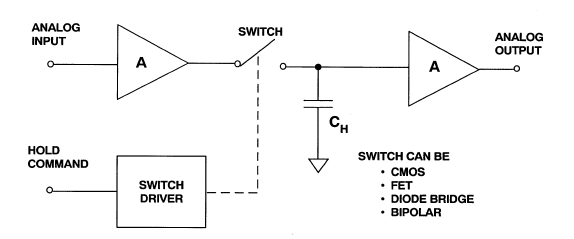

SHA�ܹ�

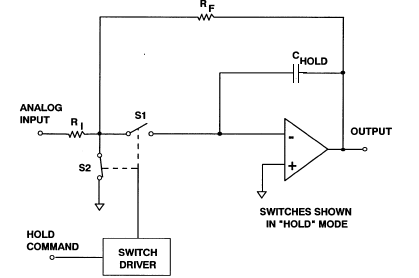

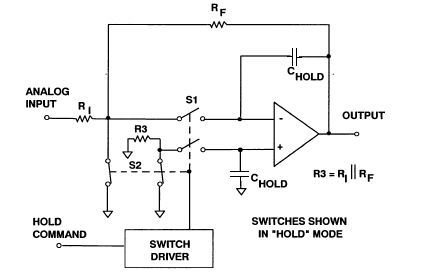

������Ŵ���һ����SHA�ܹ��������֣����ǽ���������ļ��ּܹ������SHA�ṹ��ͼ15��ʾ�������ź��ɷŴ������壬Ȼ��ʩ���ڿ��ء����뻺���������ǿ�����ջ��������ṩ���ṩ���档���ؿ�����CMOS��FET��˫���ԣ�ʹ������������ܣ����ɿ�����������·���ơ����ֵ����ϵ��ź�������Ŵ������塣��ʱ�����ּܹ���Ϊ�����ܹ�����Ϊ���ز��ڷ�����·֮�ڡ�ע�⣬ȫ���źŵ�ѹ��ʩ���ڿ��أ������������г�ɫ�Ĺ�ģ���ԡ�

ͼ15������SHA�ܹ�

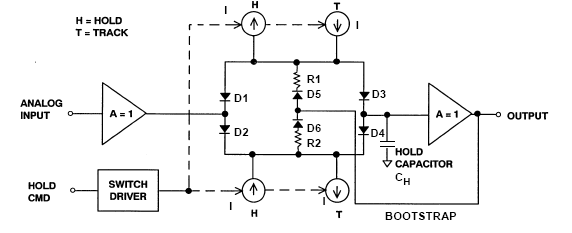

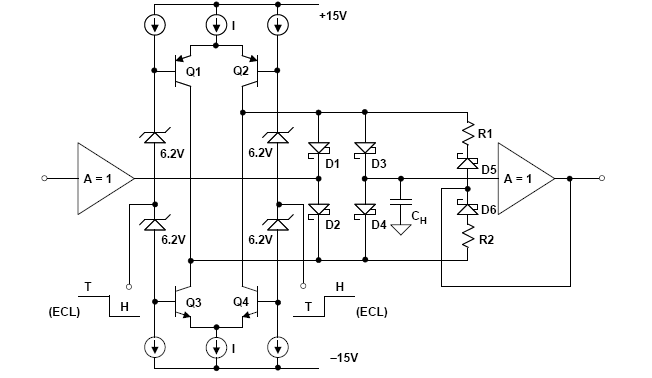

ͼ16��ʾ�����ּܹ���һ��ʵ�ַ��������п���ʹ�üĶ������š��ڸ���ģʽ�£�����������������D1��D2��D3��D4�����ڿ���ѹ�ڵ������źţ����ֵ���ͨ������I���ͷŵ硣��ˣ����ֵ��ݵ����ѹ���ʵ���I/CH��ʹ����������������ᵼ�µ��ŷ���ƫ�ã��Ӷ�����·���ڱ���ģʽ�����ñ�������ź��Ծٹر��������ʹ��ģʧ�������С������ڸõ�·������Ҫ����ƫ���ŵ�ѹ����D5��D6������ѹ�����ϴ�������R1��R2�ϵ�ѹ�����õ�·�ٶȷdz��죬�ر��������������������Ϊ���������������Ҷ�����ΪФ�ػ������ܡ��ر�����������ø�Ƶ�����ѹ����������ز�������ͼ17��ʾ���õ�·�������κβ���������ʹ�ã���Ϊ�����ܿ�������ֱ����ϵ����š���������60������������ֵ�·�IJ�ͬ��ʽ�������ڸ���PC�塢ģ��ʽ����Ϻ�IC SHA��

ͼ16��ʹ�ö������ſ��صĿ���SHA

ͼ17������SHAʵ�ַ���

ͼ18��ʾ��SHA��·�Ǿ���ıջ���ƣ��ѱ�����CMOS����ADC���á����ڿ���ʼ������ع�������˿����ϲ����ڹ�ģ�źš�

ͼ18�����ڷ���������ıջ�SHA������͵��л�

����S2�DZ���ģ����Ա��ֺ㶨�������迹����ֹ�����ź��ڱ����ڼ���ϵ�����ˡ��ڸ���ģʽ�£�SHA�Ĵ�������������Ŵ������������ز�������ֱ������Ϊ����λ�ڷ�����·֮�ڡ�����ͼ19��ʾ�IJ�ֿ��ؼ��������Խ����ע���Ӱ�콵����С��

ͼ19����ֿ��ؼ��ٵ��ע��

IC ADC������SHA��·

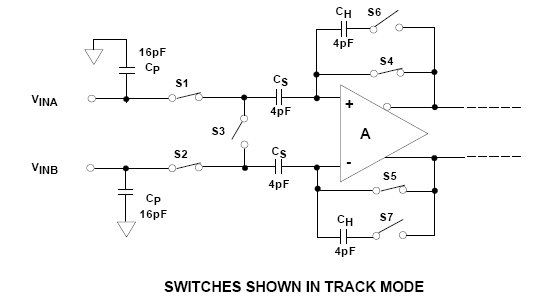

CMOS ADC���ڵ��ĺ͵ͳɱ������ܻ�ӭ��ʹ�ò�ֲ����������ĵ���CMOS ADC�ĵ�Ч�����·��ͼ20��ʾ��ͼ�п�����ʾΪ����ģʽ����Ӧע�⣬�����Բ���Ƶ�ʶϿ��ͱպϡ�16 pF���ݴ�������S1��S2����Ч�����Լ���ɢ������ݡ�CS����(4 pF)�Dz������ݣ�CH�����DZ��ֵ��ݡ���Ȼ�����·��ȫ�Dz��ʽ������ADC�ṹ�ȿ��Ե��˷�ʽ������Ҳ���Բ�ַ�ʽ������Ȼ����ʹ�ò�ֱ�ѹ�������˷�����һ����Ի��������ܡ�

ͼ20�����Ϳ��ص���CMOS �����������ļ������·

�ڸ���ģʽ�£���������ѹʩ����CS���ݡ�����·���뱣��ģʽʱ�����������ϵĵ�ѹת�Ƶ�CH���ֵ����ϣ��ɷŴ���A���壨�������ʵ��IJ���ʱ����λ���ƣ�����SHA���ظ���ģʽʱ������Դ���뽫CS�ϵĵ�ѹ����ŵ絽�µ������ѹ��CS�����ֳ��ͷŵ綯������һ��ʱ���ڵ�ƽ��ֵ���Ը����IJ���Ƶ��fs���У���ʹ�����迹����Ϊһ������������Ԫ����Ȼ��������ڲ�������(1/fs)�ڷ����ö����������迹���Ƕ�̬�ģ����뿼����������Դ��һЩע�����

�����迹�����Բ��ֿ���ͨ������CH����������Դ��ȡ��ƽ����ɶ���������Կ���������ڿ���S1��S2��֮ǰ��CS��ȫ����������ѹ����ô��������˵�ƽ�������������������֮��������һ������1/(CSfS)�ĵ��衣����CS��Ϊ��pF����˵�fS = 10 MSPSʱ�����Բ���ͨ��������k����

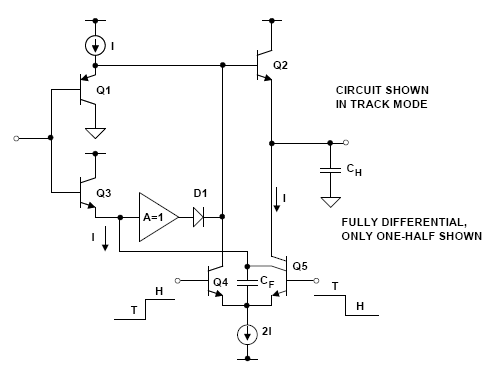

ͼ21��ʾ��1995���Ƴ���12λ41 MSPS ADC AD9042 ���õ�����SHA�ļ�·���ο�����7���� AD9042���ø��ٻ���˫���Թ���(XFCB)���졣��·�������������IJ���SHA������ȫ��ֹ�����ʽ��ͼ�н���ʾ��һ���·��ȫ��ֹ�����ʽ���Լ�С�½����������ͬʱ���ܽ��Ͷ���ʧ�档�ڸ���ģʽ�£������Q1��Q2�ṩ��λ���滺�塣����·�����ڱ���ģʽʱ��Q2�Ļ�����ѹ��������ֵ��ֱ����������D1��λ��Ƭ�ڱ��ֵ���CH�ı��ֵΪ6 pF��Q3��CFһ���ṩ��������Ծٹ��ܣ�����СQ2��VBE�仯���������������ź�ʧ�档20 MHzʱ������ģʽTHDͨ��Ϊ�C93 dB����ʱ���У�12λ���ȵ������̻�ȡʱ��Ϊ8 ns���ڱ���ģʽ�£�Q3��A = 1�������ĵ�ѹ�Ծٶ�����Q2�ĵ���ͨ����ЧӦһ��ʹ�ź���صĻ��ױ仯��С����12λ���ȵı���ģʽ����ʱ��Ϊ5 ns����50 MSPSʱ�����ʺ�20 MHz�����ź��£�����ģʽTHDΪ�C90 dB��

ͼ21��1995���Ƴ���12λ41 MSPS ADC AD9042���õ�SHA

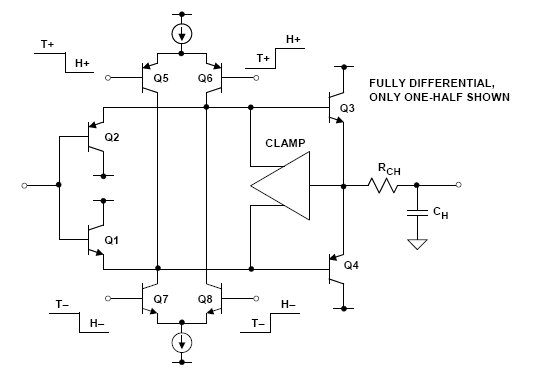

ͼ22��ʾΪ�����Ƴ���14λ105 MSPS ADC AD6645��ʹ�õIJ��SHAһ���·��ԭ��ʾ��ͼ���ο�����9��ϸ�����˸�ADC������SHA�����ڸ���ģʽ�£�Q1��Q2��Q3��Q4�γ�һ�������伫���������������������ֵ���CH���ڱ���ģʽ�£�Q3��Q4�Ļ������Է�ת����λ�ڵ��迹���Ӷ��ر�Q1��Q2��Q3��Q4������������ź��뱣�ֵ���֮�����˫�ظ��롣��ǰ��������λ��ѹ�ɱ��������ѹ�Ծ٣��Ա����̶ȵؼ�С������ЧӦ��

����ģʽ���Զ���Ҫȡ����CH���ʱQ3��Q4��VBE���ơ�����ģʽ���Զ�ȡ���ڸ���ģʽ���ԶȺ���ת����ʱ�ķ�����������÷���������ԭ����Q3��Q4�Ļ�����ѹ�л���ƽ�⣬�Լ��ɴ˵��µ�Q3��Q4�ر�ʱͨ�������-�伫��ע��ĵ�ɲ�ƽ�⡣

ͼ22��2000���Ƴ���14λ105 MSPS ADC AD6645���õ�SHA

SHAӦ��

Ŀǰ��˵��SHA�����Ӧ��������ADC������������źŴ������ִ�ADC���Dz���ADC���������ת������ƶ��Ż���SHA������ADC��ֱ���ͽ������ܾ�����ȫ��ȷ�ģ�ֻҪ�п��ܣ���Ӧ��ȡ������ʽSHA/ADC��ϡ����ڼ��ٵ�����£��ر�����ЩҪ�����̬��Χ�͵�ʧ���Ӧ�ã�ʹ�÷�����Ͽ����������ġ�

ͼ23��ʾ��һ�����Ƶ�Ӧ�ã������õ�ʧ��SHA�����ʹ������DACë�̵�Ӱ�졣����Ҫ��������������DAC֮ǰ����SHA���ڱ���ģʽ���Ӷ���DAC����ë����������롣SHA�����Ŀ���˲��������أ������Ը���Ƶ�ʳ��֣���˺����������˳������ּ����ڵ�Ƶʱ�������ã����Ը���DAC��ʧ�����ܣ�������ר��ΪDDSӦ�ö���ơ���������Ϊ����MHz�ĸ��ٵ�ë�̵�ʧ��DAC����ֵ��

ͼ23��SHA����DAC�ޱ���

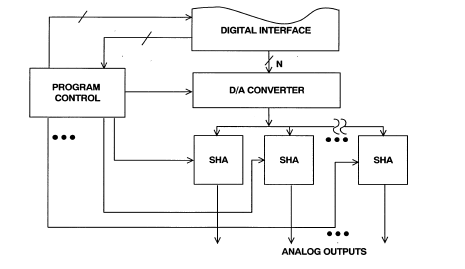

��ͬ������ϵͳ�У���ÿͨ��ʹ��һ��ADC�ķ�����ȣ�ʹ�ö��SHA��һ��ģ���·�������͵���ADC�ķ����������߾����ԣ�ͼ24����ͬ���������ݷ���ϵͳ�У�����ʹ�ö��SHA������DAC��˳�����·�ɵ����ͨ������ͼ25��ʾ��������������̫�ձ飬��Ϊʹ�ö��DAC�ķ���ͨ�����á�

ͼ24��ʹ�ö�� SHA�͵���ADC��ͬ������

ͼ25��ʹ�ö��SHA�͵���DAC�����ݷ���ϵͳ

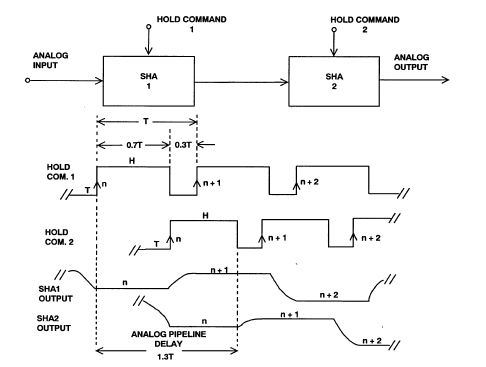

SHA�����һ��Ӧ����ͼ26��ʾ����һ�����ݲ���ϵͳ�У����SHA���������Բ���ģ���ӳ١���SHA 1�ı��ּ��ʱ���Ҫ����֮ǰ��SHA 2�����ڱ���ģʽ����ˣ�����ˮ���ӳ�ʱ����ڲ�������T�����ּ����������ڶ༶��ˮ��ʽ�ּ�ADC�У����ṩ�����༶��ת���ӳ١�����ˮ��ʽADC�У�50%ռ�ձȵIJ���ʱ�Ӻ��ձ飬����������ý����ʱ����λ��������ˮ���еĸ�SHA����ˮ��ʽADC����̳�MT-024����

ͼ26�����ڲ���ģ����ˮ���ӳٵ�SHA

- ��һƪ����߳��ͣ�ʵ��ƽ�ȵ�Ƿѹ��ѹ���� [2021-11-18]

- ��һƪ�����ѡ����ʵĵ�·���� [2021-11-17]